-

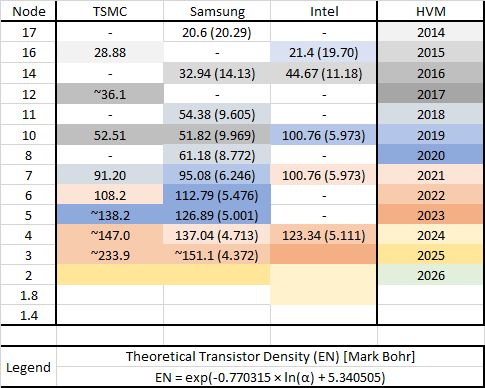

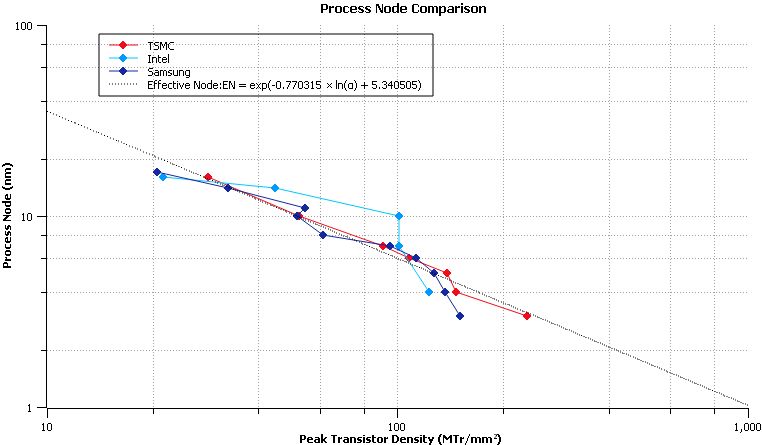

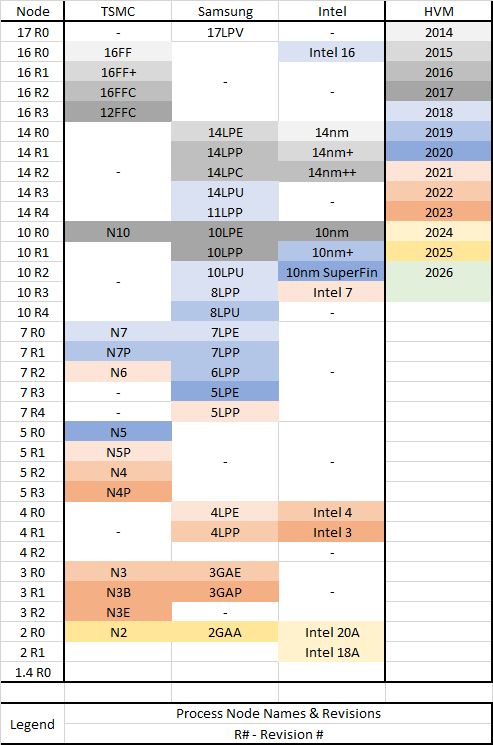

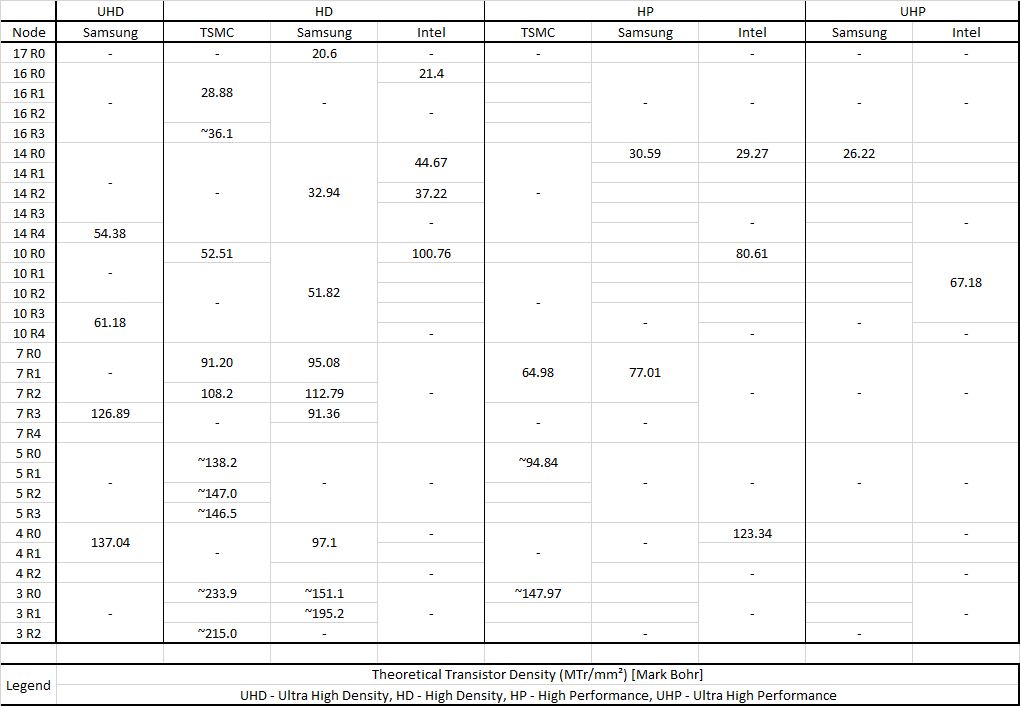

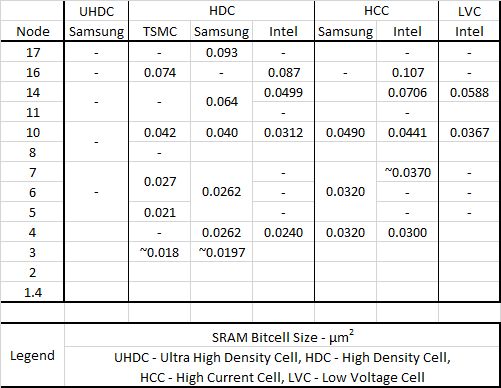

Fun Facts: For every 2x shrink in node name, there's ~1.7x shrink in density. TSMC states +6% density on N4P, but also -6% area on N4, meaning a naive calculation says N4 is denser. Samsung added UHD SRAM with 5LPP and continued it on 4LPE, but has yet to reveal its size.

-

Bonuses for anyone that follows me: Samsung 3GAP: ~195.2 TSMC N3E: ~215.9 There's also a mistake in N3, it should be ~234.9, not ~233.9.

-

Small Update, I had completely missed out on this, but TSMC disclosed the HP (HCC) SRAM bitcell size on N5, its 0.025 μm², making it the third densest bitcell disclosed to date, after only N5 HD and I4 HD.

Redfire75369’s Twitter Archive—№ 3,384

Redfire75369’s Twitter Archive—№ 3,384