Most Recent 40 Tweets

Not including replies or retweets or mentions.

Tweets

-

Well, there goes twitter. You know where to find me. Most likely my last tweet. Not deleting my account or anything but there it goes.

-

Apparently Intel Lab's 49 qubit chip is called Tangle Lake, you've got to be kidding me. For those who are missing it, it's a nod to the qubits being entangled with one another.

-

Intel Sapphire Rapids-80L/W/X: Xeon W 34xx - 8ch DDR5 Xeon W 24xx - 4ch DDR5 @OneRaichu/1596450453210161152

-

Bump. The situation just gets worse and worse. @Redfire75369/1592954808121847808

-

Since the current platform is quickly approaching "depreciation": Mastodon: mastodon.online/@redfire Cohost: cohost.org/redfire

-

Ignoring the content of the tweet, for I couldn't care less, All this continues to show is that leaks should all be thrown in the trash, even if they look legitimate. Stop taking leaks so seriously, and acting as if your life is ruined when they inevitably turn out wrong. @davidbepo/1590996355807588354

-

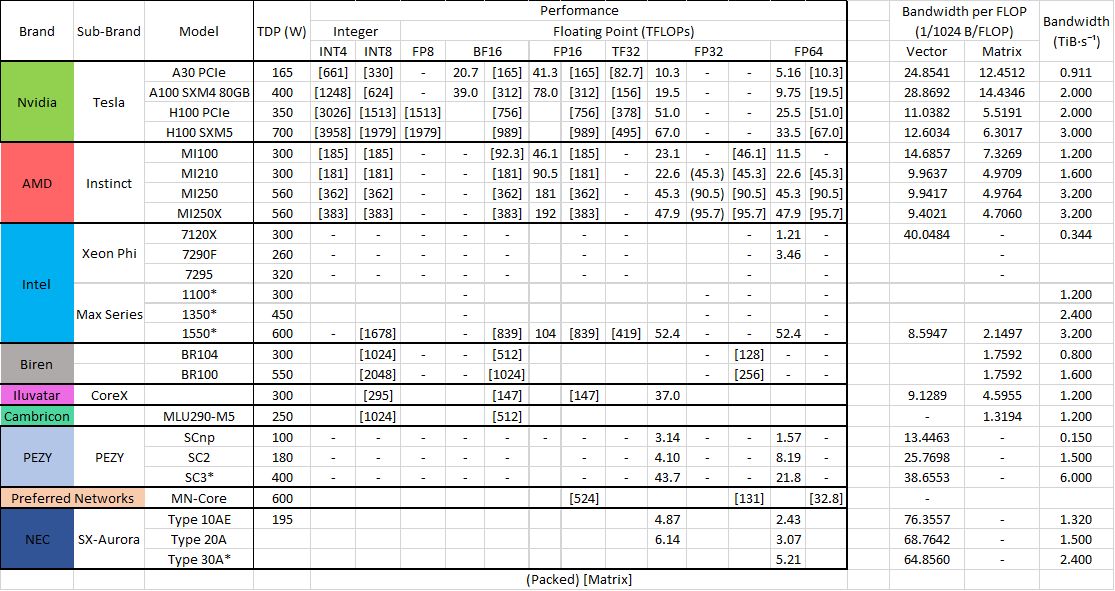

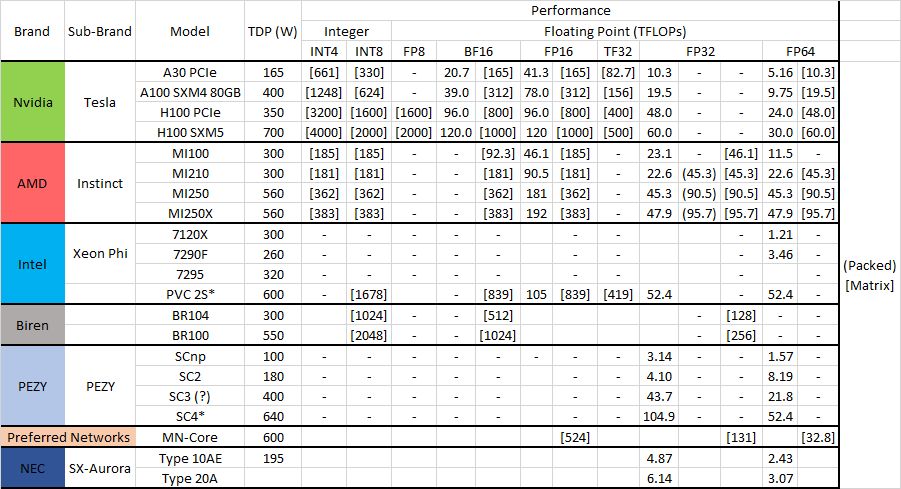

With the announcement of the Intel GPU Max Series (Ponte Vecchio), I have updated the performance table yet again. For the first time, bandwidth per FLOP is shown too. Ponte Vecchio is on the GPU spreadsheets now: silicon.redfire.dev/spreadsheets/gpus/

-

Most semiconductor companies are cutting their capex and/or guidances, yet more and more capital projects are still being announced. I went through the past 3 months and already got ~15 new ones.

-

Pete del Vecchio is the product line manager for the Broadcom Tomahawk 5. Coincidence? I think not. Maybe it has special integration with Ponte Vecchio. 😛

-

As I said, everyone is being played. chipsandcheese.com/2022/10/27/why-you-cant-trust-cpuid/ @Redfire75369/1585577180007841792

-

Be wary, for everyone is currently being played.

-

Support for libfabric means it can probably be used with Omni-Path Express, I think. Time for Intel DAOS + Cornellis OPX. @phoronix/1583756942459084800

-

Important Milestone for @fasterthanlime 420 Public Repositories Who knows how many are private

-

So I've been working on a HTTP module for @spiderfirejs (just a client for now), and I'm thinking if I should implement any more default headers than just the host and optionally authorisation.

-

Although cool that Micron is coming to New York, companies really need to be stopped from claiming huge investments over decades. @MicronTech/1577293535958732802

-

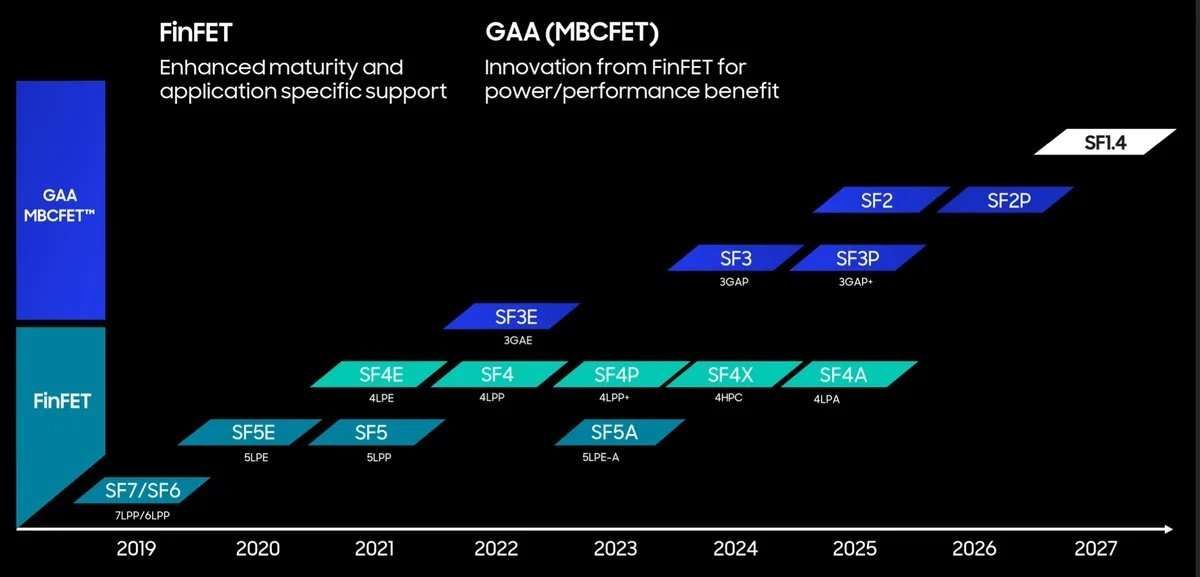

Pretty much standard, based on what we've known so far. Wasn't expecting a 4HPC node, but given 7HPP, not that outlandish. The lack of a 3GA# node in 2023 makes me hopeful they're trying to fix their issues internally. @Samsung/1577153863546986496

-

Intel Alder Lake-N Core i3-N105 Cores: 8C/8T Gracemont Base/Boost: 1.8 GHz/3.7 GHz L1I/D: 64 KiB/32 KiB L2: 2MiB/cluster L3: 6MiB (3MiB/cluster) @BenchLeaks/1575330200086257664

-

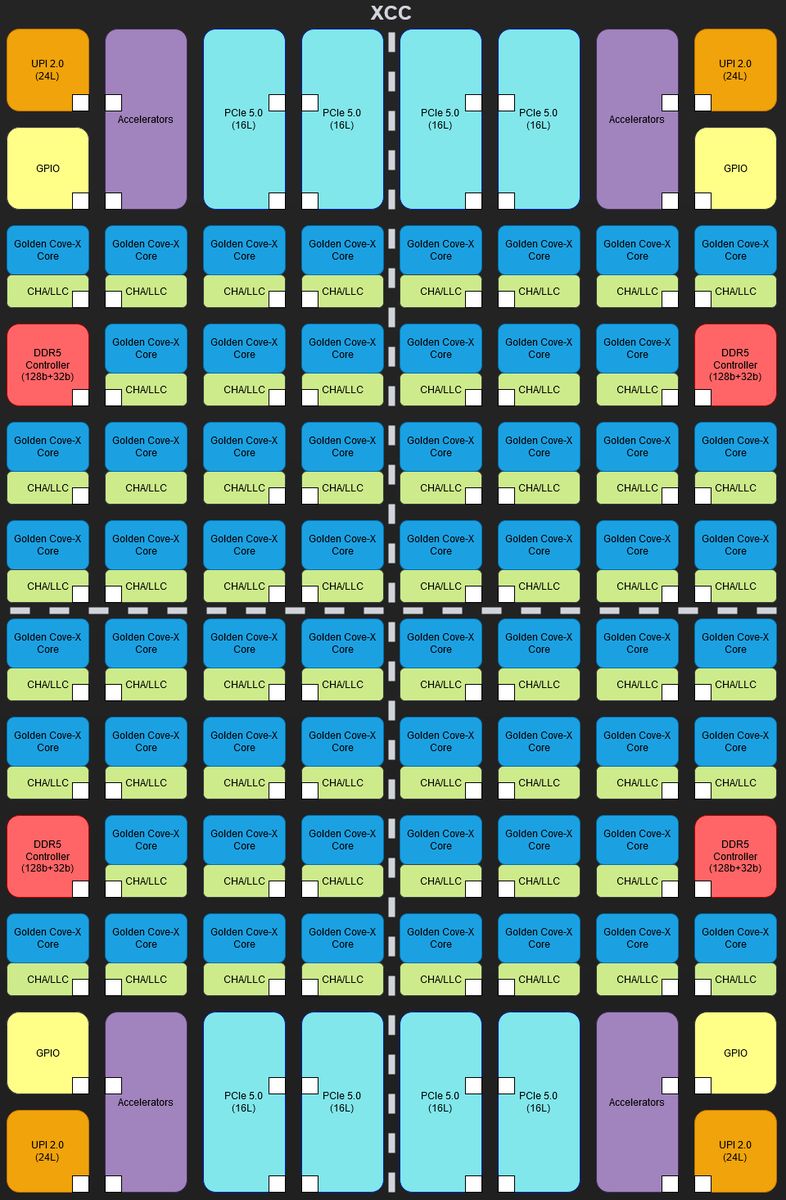

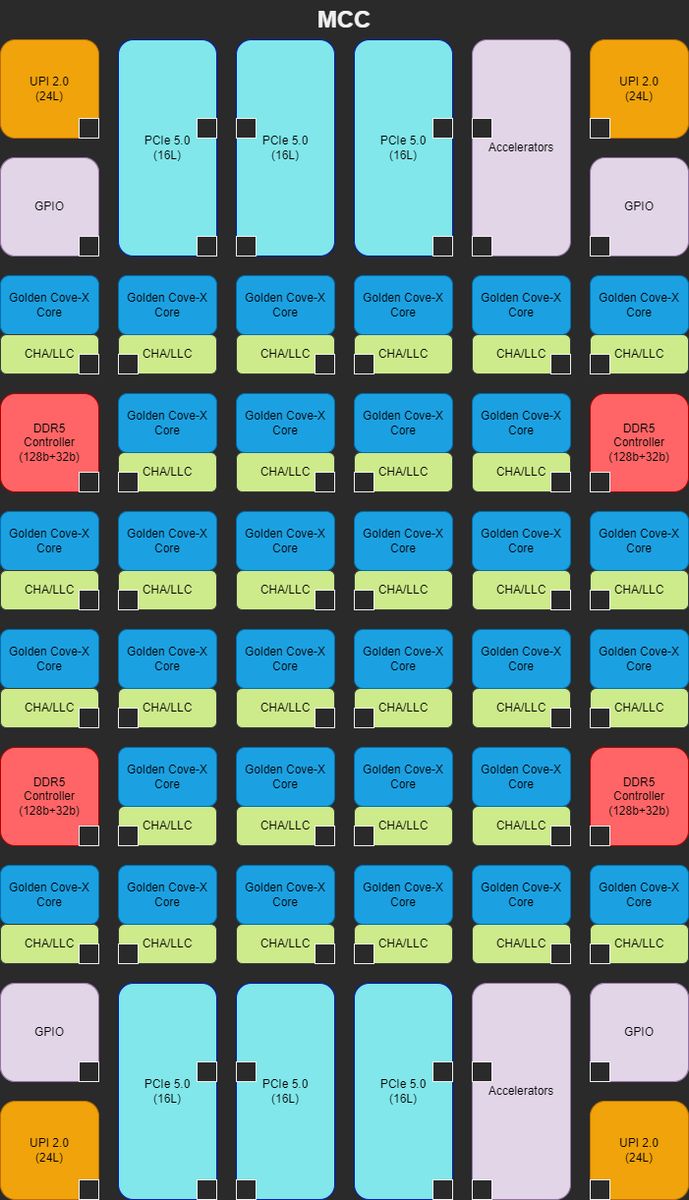

BIG Site Update: I've updated all the spreadsheets and updated the mesh diagram for Sapphire Rapids MCC. SPR Mesh: silicon.redfire.dev/diagrams/mesh/sapphire-rapids/ CPUs: silicon.redfire.dev/spreadsheets/cpus/ GPUs: silicon.redfire.dev/spreadsheets/gpus/

-

"Intel 4 can't have monolithic dies" @ItsABitRISCV/1574945058901692416

-

I did not see this mesh layout coming, I'll update the site later today. @IanCutress/1574950751679283201

-

34C MCC Die for SPR I'm not sure if it's WS only or for Server too, but here's some confirmation. @tomshardware/1574946519496654849

-

As I was saying, part of removing the Celeron and Pentium branding. Not sure what they'll call the 8C though. @BenchLeaks/1574221132101783554

-

This makes a lot more sense now, restarting the naming of the whole lineup, starting with the Intel Processor N100. I don't exactly like the branding, but I see why they felt like they had to change it.O @InstLatX64/1558386372934778880

-

24GB HBM3 was expected anyways 12-Hi stack with 16Gb dies. The limit is 64GB so we're still a long ways away. @HotHardware/1574526473129582621

-

Called this months ago, and here there were people saying "Nvidia couldn't make a chip with such new cores so soon after launch". @aschilling/1570049742754779137

-

> The company [SiFive] has deals with Renesas and Intel’s Mobileye subsidiary to use RISC-V cores in automotive driver assistance ADAS chips with support from (...) eenewseurope.com/en/sifive-rolls-out-automotive-risc-v-roadmap/

-

Continued Software Acquisitions for oneAPI and more, Ananki (ONF), Linutronix, Codeplay and now Arrayfire. They also bought Granulate, Siru, Screenovate, RemoteMyApp. @JamesReinders/1567980740264230913

-

Not only is this bad, it's intentionally misleading and blatantly anti-consumer. Important Information (Zen X) is hidden near the end. Consumers are lazy and generally only look at the start when buying chips. @ComputerBase/1567497924149481475

-

Small addition to the site, capability to display .drawio diagrams. I've uploaded the diagrams for the meshes of ICX-SP and SPR-SP. ICX-SP: silicon.redfire.dev/diagrams/mesh/ice-lake/ SPR-SP: https://t.co/nsuaTFfVbP

-

After staring at the Sapphire Rapids-HBM package for way too long, I think that the HBM controllers use the mesh stops that belong to the accelerators in regular SPR, meaning SPR-HBM won't have QAT or DSA.

-

The code for my website is now open source! Or at least visible source... I don't know yet It doesn't include the MD(X) files or the spreadsheets for now, until I feel like publishing those. github.com/Redfire75369/silicon

-

I've just gotten my own domain and have moved my site to it, so I guess a bunch of links I have sent might be broken now. silicon.redfire.dev/

-

Well that's fun... Battlemage's largest die should have almost 30KB/cycle of bandwidth from L2... I guess that's how Intel is planning to address bandwidth requirements on future GPUs.

-

Today's Fun Fact: Winbond had more CapEx than UMC in 2Q22. For some reason, Winbond also has a higher market cap. @Redfire75369/1557376016623882241

-

I did not think this would happen before launch, but @spiderfirejs has now reached 100 stars! github.com/Redfire75369/spiderfire

Redfire75369’s Twitter Archive

Redfire75369’s Twitter Archive