-

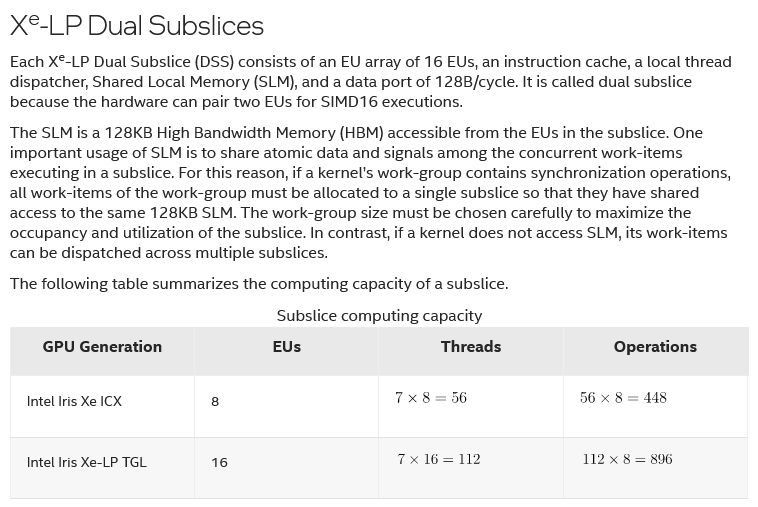

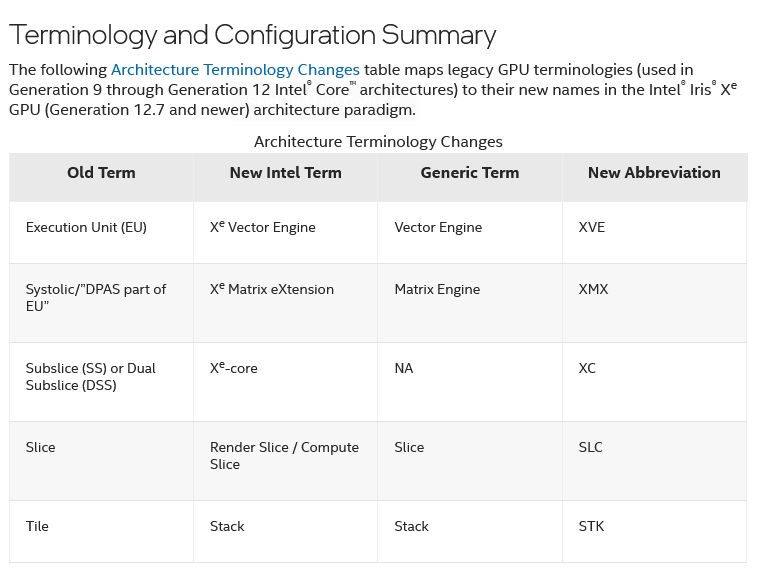

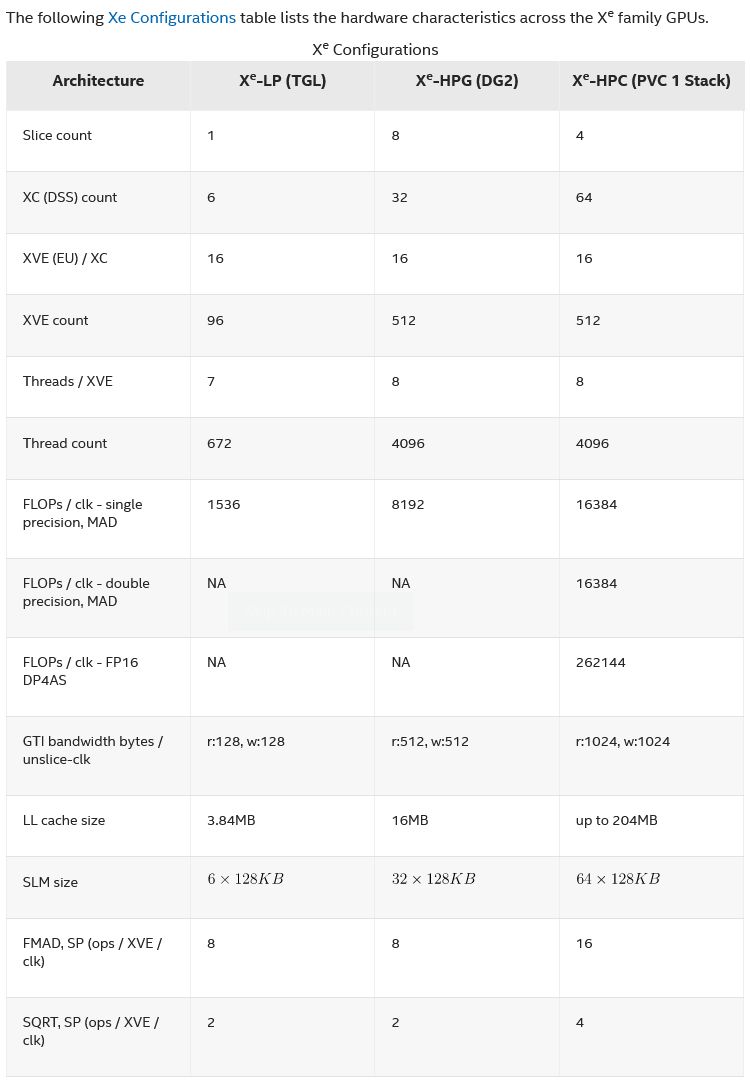

Interesting Section about Xe on the Developer Guide for oneAPI: This talks about Xe-LP, Xe-HPG and Xe-HPC. This mostly talks about architectural details, although its not super low-level either. 🧵(1/x) intel.com/content/www/us/en/develop/documentation/oneapi-gpu-optimization-guide/top/xe-arch.html

-

Xe-HPG does not support FP16 DP4AS, seemingly, which is weird. It also shows that Xe-HPC is 2x performance/XVE/clock in everything because of the fused dual EU, though that's obvious. (5/5)

Redfire75369’s Twitter Archive—№ 2,863

Redfire75369’s Twitter Archive—№ 2,863